#### PENTIUM® PROCESSOR at iCOMP® INDEX 610\75 MHz

- Compatible with Large Software Base

- MS-DOS\*, Windows\*, OS/2\*, UNIX\*

- 32-Bit CPU with 64-Bit Data Bus

- Superscalar Architecture

- Two Pipelined Integer Units Are Capable of 2 Instructions/Clock

- Pipelined Floating Point Unit

- Separate Code and Data Caches

- 8K Code, 8K Writeback Data

- MESI Cache Protocol

- Advanced Design Features

- Branch Prediction

- Virtual Mode Extensions

- 3.3V BiCMOS Silicon Technology

- 4M Pages for Increased TLB Hit Rate

- IEEE 1149.1 Boundary Scan

- Internal Error Detection Features

- SL Enhanced Power Management Features

- System Management Mode

- Clock Control

- **■** Fractional Bus Operation

- 75-MHz Core / 50-MHz Bus

The Pentium® processor is fully compatible with the entire installed base of applications for DOS\*, Windows\*, OS/2\*, and UNIX\*, and all other software that runs on any earlier Intel 8086 family product. The Pentium processor's superscalar architecture can execute two instructions per clock cycle. Branch prediction and separate caches also increase performance. The pipelined floating-point unit delivers workstation level performance. Separate code and data caches reduce cache conflicts while remaining software transparent. The Pentium processor (610\75) has 3.3 million transistors, is built on Intel's advanced 3.3V BiCMOS silicon technology, and has full SL Enhanced power management features, including System Management Mode (SMM) and clock control. The additional SL Enhanced features, 3.3V operation, and the TCP package, which are not available in the Pentium processor (510\60, 567\66), make the Pentium processor (610\75) TCP ideal for enabling mobile Pentium processor designs. The Pentium processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available upon request.

June 1997 Order Number 242323-004

### **CONTENTS**

| PAGE                                                                  | PAGE                                         |

|-----------------------------------------------------------------------|----------------------------------------------|

| 1.0. INTRODUCTION2                                                    | 4.3. AC Specifications25                     |

| 1.1. Pentium® Processor (610\75) SPGA                                 | 4.3.1. POWER AND GROUND25                    |

| Specifications and Differences from the TCP Package2                  | 4.3.2. DECOUPLING RECOMMENDATIONS25          |

| 1 dolago                                                              | 4.3.3. CONNECTION SPECIFICATIONS26           |

| 2.0. MICROPROCESSOR ARCHITECTURE                                      | 4.3.4. AC TIMINGS FOR A 50-MHZ BUS26         |

| OVERVIEW3                                                             | 4.4. I/O Buffer Models35                     |

| 2.1. Pentium® Processor Family Architecture4                          | 4.4.1. BUFFER MODEL PARAMETERS38             |

| 3.0. TCP PINOUT7                                                      | 4.4.2. SIGNAL QUALITY SPECIFICATIONS .39     |

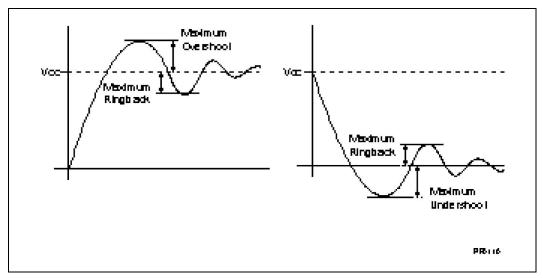

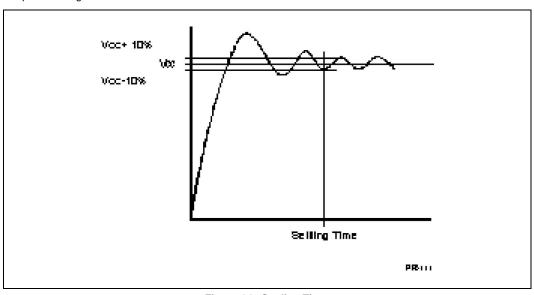

| 3.1. TCP Pinout and Pin Descriptions7                                 | 4.4.2.1. Ringback40                          |

| 3.1.1. Pentium® Processor (610\75) TCP                                | 4.4.2.2. Settling Time40                     |

| PINOUT7                                                               | 5.0. Pentium® Processor (610\75) TCP         |

| 3.1.2. PIN CROSS REFERENCE TABLE FOR Pentium® Processor (610\75) TCP8 | MECHANICAL SPECIFICATIONS42                  |

| 3.2. Design Notes10                                                   | 5.1. TCP Package Mechanical Diagrams42       |

| 3.3. Quick Pin Reference10                                            | 6.0. Pentium® Processor (610\75) TCP THERMAL |

| 3.4. Pin Reference Tables19                                           | SPECIFICATIONS47                             |

| 3.5. Pin Grouping According to Function22                             | 6.1. Measuring Thermal Values47              |

|                                                                       | 6.2. Thermal Equations47                     |

| 4.0. Pentium® Processor (610\75) TCP ELECTRICAL SPECIFICATIONS23      | 6.3. TCP Thermal Characteristics47           |

|                                                                       | 6.4. PC Board Enhancements47                 |

| 4.1. Maximum Ratings                                                  | 6.4.1. STANDARD TEST BOARD CONFIGURATION48   |

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Pentium® processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 7641

Mt. Prospect IL 60056-7641

or call 1-800-879-4683

or visit Intel's website at http://www.intel.com

Copyright © Intel Corporation 1996, 1997.

<sup>\*</sup> Third-party brands and names are the property of their respective owners.

#### 1.0. INTRODUCTION

Intel is now manufacturing its latest version of the Pentium® processor family that is designed specifically for mobile systems, with a core frequency of 75 MHz and a bus frequency of 50 MHz. The Pentium processor (610\text{\text{75}}) is provided in the TCP (Tape Carrier Package) and SPGA packages, and has all of the advanced features of the Pentium processor (735\90, 815\100).

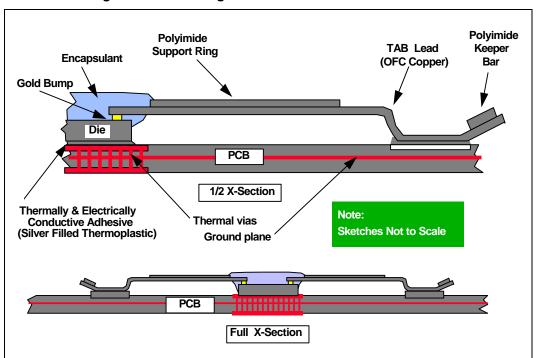

The new Pentium processor (610\75) TCP package has several features which allow high-performance notebooks to be designed with the Pentium processor, including the following:

- TCP package dimensions are ideal for small form-factor designs.

- The TCP package has superior thermal resistance characteristics.

- 3.3V V<sub>CC</sub> reduces power consumption by half (in both the TCP and SPGA packages).

- The SL Enhanced feature set, which was initially implemented in the Intel486™ CPU.

The architecture and internal features of the Pentium processor (610\75) TCP and SPGA packages are identical to those of the Pentium processor (735\90, 815\100), although several features have been eliminated for the Pentium processor (610\75) TCP, as described in section 1.1.

This document should be used in conjunction with the Pentium processor documents listed below. List of related documents:

- Pentium® Processor Family Developer's Manual, Vol. 1 (Order Number: 241428)

- Pentium® Processor Family Developer's Manual, Vol. 3: Architecture and Programming Manual (Order Number: 241430)

#### 1.1. Pentium® Processor (610\75) SPGA Specifications and Differences from the TCP Package

This section provides references to the Pentium processor (610\75) SPGA specifications and describes the major differences between the Pentium processor (610\75) SPGA and TCP packages.

All Pentium processor (610\75) SPGA specifications, with the exception of power consumption, are identical to the Pentium processor (735\90, 815\100) specifications provided in the Pentium® Processor Family Developer's Manual, Volume 1. See Tables 8 and 11 in section 4.2 for the Pentium processor (610\75) SPGA and TCP power specifications.

The following features have been eliminated for the Pentium processor (610\75) TCP: the Upgrade feature, the Dual Processing (DP) feature, and the Master/Checker functional redundancy feature. Table 1 lists the corresponding pins which exist on the Pentium processor (610\75) SPGA but have been removed on the Pentium processor (610\75) TCP.

Table 1. SPGA Signals Removed in TCP

| Signal | Function                                                                                                                                                                |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADSC#  | Additional Address Status. This signal is mainly used for large or standalone L2 cache memory subsystem support required for high-performance desktop or server models. |

| BRDYC# | Additional Burst Ready. This signal is mainly used for large or standalone L2 cache memory subsystem support required for high-performance desktop or server models.    |

| CPUTYP | CPU Type. This signal is used for dual processing systems.                                                                                                              |

| D/P#   | Dual/Primary processor identification. This signal is only used for an Upgrade processor.                                                                               |

| FRCMC# | Functional Redundancy Checking. This signal is only used for error detection via processor redundancy, and requires two Pentium processors (master/checker).            |

| PBGNT# | Private Bus Grant. This signal is only used for dual processing systems.                                                                                                |

| PBREQ# | Private Bus Request. This signal is used only for dual processing systems.                                                                                              |

| PHIT#  | Private Hit. This signal is only used for dual processing systems.                                                                                                      |

| PHITM# | Private Modified Hit. This signal is only used for dual processing systems.                                                                                             |

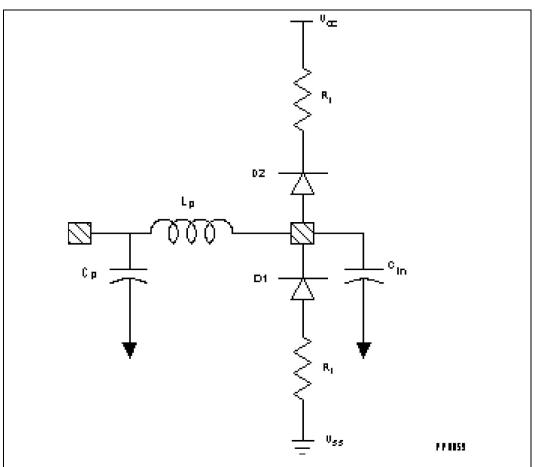

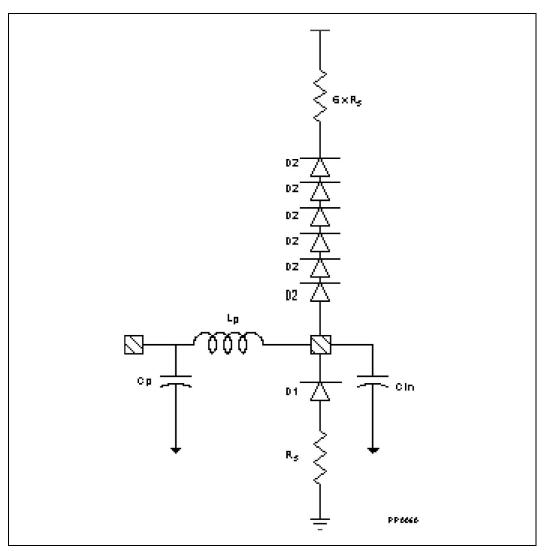

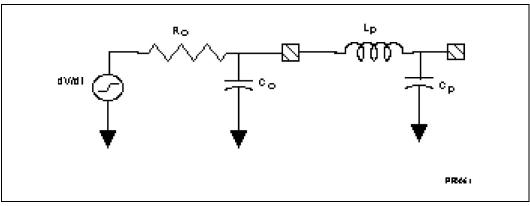

The I/O buffer models provided in section 4.4 of this document apply to both the Pentium processor (610\75) TCP and SPGA packages, although the capacitance ( $C_p$ ) and inductance ( $L_p$ ) parameter values differ between the two packages. Also, the thermal parameters,  $T_{CASE}$  max and  $\theta_{CA}$ , differ between the TCP and SPGA packages. For Pentium processor (610\75) SPGA values, refer to Chapters 24 and 26 of the  $Pentium^{\circledast}$  Processor Family Developer's Manual, Volume 1 .

# 2.0. MICROPROCESSOR ARCHITECTURE OVERVIEW

The Pentium processor at iCOMP® rating 610\75 MHz extends the Intel Pentium family of microprocessors. It is compatible with the 8086/88, 80286, Intel386™ DX CPU, Intel386 SX CPU, Intel486™ DX CPU, Intel486 SX CPU, Intel486 DX2 CPUs, the Pentium processor at iCOMP Index 510\60 MHz and iCOMP Index 567\66 MHz, and the Pentium processor at iCOMP Index 735\90 MHz and iCOMP Index 815\100 MHz.

The Pentium processor family consists of the new Pentium processor at iCOMP rating 610\75 MHz, described in this document, the original Pentium processor (510\60, 567\66), and the Pentium processor (735\90, 815\100). The name "Pentium

processor (610\75)" will be used in this document to refer to the Pentium processor at iCOMP rating 610\75 MHz. "Pentium Processor" will be used in this document to refer to the entire Pentium processor family in general.

The Pentium processor family architecture contains all of the features of the Intel486 CPU family, and provides significant enhancements and additions including the following:

- Superscalar Architecture

- Dynamic Branch Prediction

- Pipelined Floating-Point Unit

- Improved Instruction Execution Time

- Separate 8K Code and 8K Data Caches

- Writeback MESI Protocol in the Data Cache

- 64-Bit Data Bus

- Bus Cycle Pipelining

- Address Parity

- Internal Parity Checking

- Execution Tracing

- Performance Monitoring

- IEEE 1149.1 Boundary Scan

- System Management Mode

Virtual Mode Extensions

# 2.1. Pentium® Processor Family Architecture

The application instruction set of the Pentium processor family includes the complete Intel486 CPU family instruction set with extensions to accommodate some of the additional functionality of the Pentium processors. All application software written for the Intel386 and Intel486 family microprocessors will run on the Pentium processors without modification. The on-chip memory management unit (MMU) is completely compatible with the Intel386 family and Intel486 family of CPUs.

The Pentium processors implement several enhancements to increase performance. The two instruction pipelines and floating-point unit on Pentium processors are capable of independent operation. Each pipeline issues frequently used instructions in a single clock. Together, the dual pipes can issue two integer instructions in one clock, or one floating point instruction (under certain circumstances, two floating-point instructions) in one clock.

Branch prediction is implemented in the Pentium processors. To support this, Pentium processors implement two prefetch buffers, one to prefetch code in a linear fashion, and one that prefetches code according to the BTB so the needed code is almost always prefetched before it is needed for execution.

The floating-point unit has been completely redesigned over the Intel486 CPU. Faster algorithms provide up to 10X speed-up for common operations including add, multiply, and load.

Pentium processors include separate code and data caches integrated on-chip to meet performance goals. Each cache is 8 Kbytes in size, with a 32-byte line size and is 2-way set associative. Each cache has a dedicated Translation Lookaside Buffer (TLB) to translate linear addresses to physical addresses. The data cache is configurable to be

writeback or writethrough on a line-by-line basis and follows the MESI protocol. The data cache tags are triple ported to support two data transfers and an inquire cycle in the same clock. The code cache is an inherently write-protected cache. The code cache tags are also triple ported to support snooping and split line accesses. Individual pages can be configured as cacheable or non-cacheable by software or hardware. The caches can be enabled or disabled by software or hardware.

The Pentium processors have increased the data bus to 64 bits to improve the data transfer rate. Burst read and burst writeback cycles are supported by the Pentium processors. In addition, bus cycle pipelining has been added to allow two bus cycles to be in progress simultaneously. The Pentium processors' Memory Management Unit contains optional extensions to the architecture which allow 2-Mbyte and 4-Mbyte page sizes.

The Pentium processors have added significant data integrity and error detection capability. Data parity checking is still supported on a byte-by-byte basis. Address parity checking, and internal parity checking features have been added along with a new exception, the machine check exception.

As more and more functions are integrated on chip, the complexity of board level testing is increased. To address this, the Pentium processors have increased test and debug capability. The Pentium processors implement IEEE Boundary Scan (Standard 1149.1). In addition, the Pentium processors have specified 4 breakpoint pins that correspond to each of the debug registers and externally indicate a breakpoint match. Execution tracing provides external indications when an instruction has completed execution in either of the two internal pipelines, or when a branch has been taken.

System Management Mode (SMM) has been implemented along with some extensions to the SMM architecture. Enhancements to the virtual 8086 mode have been made to increase performance by reducing the number of times it is necessary to trap to a vir tual 8086 monitor.

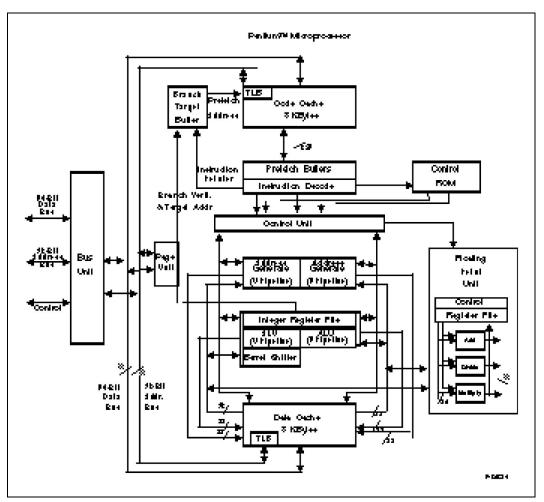

Figure 1. Pentium® Processor Block Diagram

The block diagram shows the two instruction pipelines, the "u" pipe and the "v" pipe. The u-pipe can execute all integer and floating point instructions. The v-pipe can execute simple integer instructions and the FXCH floating-point instructions.

The separate caches are shown, the code cache and data cache. The data cache has two ports, one for each of the two pipes (the tags are triple ported to allow simultaneous inquire cycles). The data cache has a dedicated Translation Lookaside Buffer (TLB) to translate linear addresses to the physical addresses used by the data cache.

The code cache, branch target buffer and prefetch buffers are responsible for getting raw instructions into the execution units of the Pentium processor. Instructions are fetched from the code cache or from the external bus. Branch addresses are remembered by the branch target buffer. The code cache TLB translates linear addresses to physical addresses used by the code cache.

The decode unit decodes the prefetched instructions so the Pentium processor can execute the instruction. The control ROM contains the microcode which controls the sequence of operations that must be performed to implement the Pentium processor architecture. The control ROM unit has direct control over both pipelines.

The Pentium processors contain a pipelined floating-point unit that provides a significant floating-point performance advantage over previous generations of processors.

The architectural features introduced in this section are more fully described in the *Pentium® Processor Family Developer's Manual*.

#### 3.0. TCP PINOUT

#### 3.1. TCP Pinout and Pin Descriptions

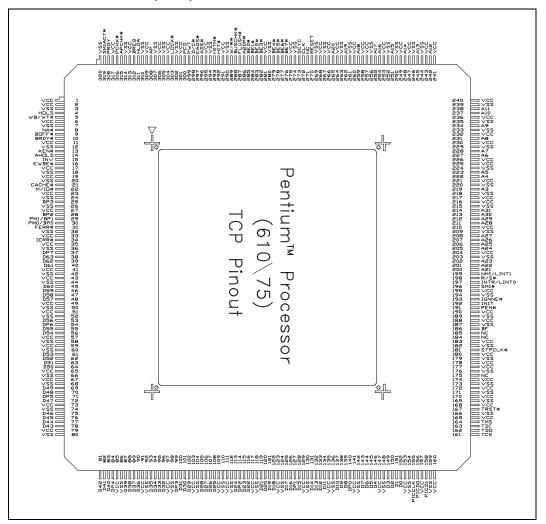

#### 3.1.1. Pentium® Processor (610\75) TCP PINOUT

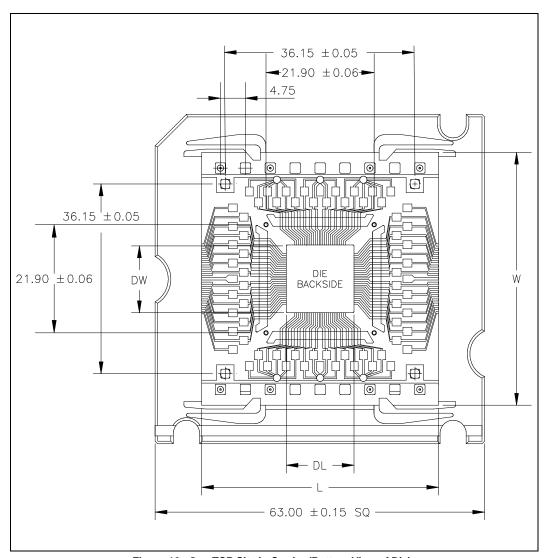

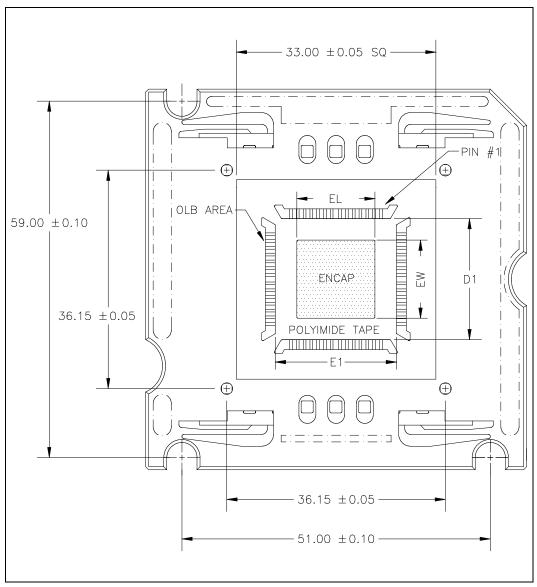

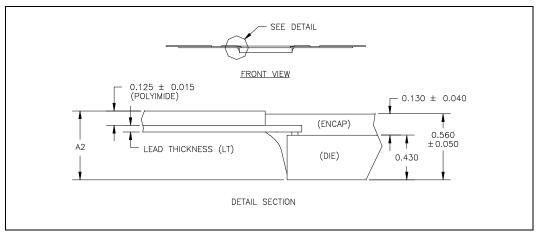

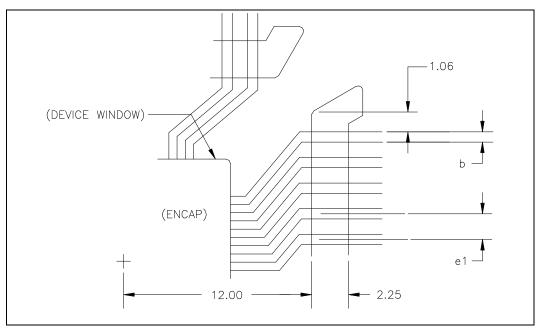

Figure 2. Pentium® Processor (610\75) TCP Pinout

## 3.1.2. PIN CROSS REFERENCE TABLE FOR Pentium® Processor (610\75) TCP

Table 2. TCP Pin Cross Reference by Pin Name

|     | Address |     |     |     |      |     |     |     |     |

|-----|---------|-----|-----|-----|------|-----|-----|-----|-----|

| A3  | 219     | A9  | 234 | A15 | 251  | A21 | 200 | A27 | 208 |

| A4  | 222     | A10 | 237 | A16 | 254  | A22 | 201 | A28 | 211 |

| A5  | 223     | A11 | 238 | A17 | 255  | A23 | 202 | A29 | 212 |

| A6  | 227     | A12 | 242 | A18 | 259  | A24 | 205 | A30 | 213 |

| A7  | 228     | A13 | 245 | A19 | 262  | A25 | 206 | A31 | 214 |

| A8  | 231     | A14 | 248 | A20 | 265  | A26 | 207 |     |     |

|     |         | 1   |     |     | Data | I   |     |     |     |

| D0  | 152     | D13 | 132 | D26 | 107  | D39 | 87  | D52 | 62  |

| D1  | 151     | D14 | 131 | D27 | 106  | D40 | 83  | D53 | 61  |

| D2  | 150     | D15 | 128 | D28 | 105  | D41 | 82  | D54 | 56  |

| D3  | 149     | D16 | 126 | D29 | 102  | D42 | 81  | D55 | 55  |

| D4  | 146     | D17 | 125 | D30 | 101  | D43 | 78  | D56 | 53  |

| D5  | 145     | D18 | 122 | D31 | 100  | D44 | 77  | D57 | 48  |

| D6  | 144     | D19 | 121 | D32 | 96   | D45 | 76  | D58 | 47  |

| D7  | 143     | D20 | 120 | D33 | 95   | D46 | 75  | D59 | 46  |

| D8  | 139     | D21 | 119 | D34 | 94   | D47 | 72  | D60 | 45  |

| D9  | 138     | D22 | 116 | D35 | 93   | D48 | 70  | D61 | 40  |

| D10 | 137     | D23 | 115 | D36 | 90   | D49 | 69  | D62 | 39  |

| D11 | 134     | D24 | 113 | D37 | 89   | D50 | 64  | D63 | 38  |

| D12 | 133     | D25 | 108 | D38 | 88   | D51 | 63  |     |     |

Table 2. TCP Pin Cross Reference by Pin Name (Contd.)

|                  | Control |          |     |            |         |         |     |  |

|------------------|---------|----------|-----|------------|---------|---------|-----|--|

| A20M#            | 286     | BREQ     | 312 | HITM#      | 293     | PM1/BP1 | 29  |  |

| ADS#             | 296     | BUSCHK#  | 288 | HLDA       | 311     | PRDY    | 318 |  |

| AHOLD            | 14      | CACHE#   | 21  | HOLD       | 4       | PWT     | 299 |  |

| AP               | 308     | D/C#     | 298 | IERR#      | 34      | R/S#    | 198 |  |

| APCHK#           | 315     | DP0      | 140 | IGNNE#     | 193     | RESET   | 270 |  |

| BE0#             | 285     | DP1      | 127 | INIT       | 192     | SCYC    | 273 |  |

| BE1#             | 284     | DP2      | 114 | INTR/LINT0 | 197     | SMI#    | 196 |  |

| BE2#             | 283     | DP3      | 99  | INV        | 15      | SMIACT# | 319 |  |

| BE3#             | 282     | DP4      | 84  | KEN#       | 13      | TCK     | 161 |  |

| BE4#             | 279     | DP5      | 71  | LOCK#      | 303     | TDI     | 163 |  |

| BE5#             | 278     | DP6      | 54  | M/IO#      | 22      | TDO     | 162 |  |

| BE6#             | 277     | DP7      | 37  | NA#        | 8       | TMS     | 164 |  |

| BE7#             | 276     | EADS#    | 297 | NMI/LINT1  | 199     | TRST#   | 167 |  |

| BOFF#            | 9       | EWBE#    | 16  | PCD        | 300     | W/R#    | 289 |  |

| BP2              | 28      | FERR#    | 31  | PCHK#      | 316     | WB/WT#  | 5   |  |

| BP3              | 25      | FLUSH#   | 287 | PEN#       | 191     |         |     |  |

| BRDY#            | 10      | HIT#     | 292 | PM0/BP0    | 30      |         |     |  |

| APIC             |         |          |     |            | Clock ( | Control |     |  |

| PICCLK           | 155     | PICD1    | 158 | BF         | 186     | STPCLK# | 181 |  |

| PICD0<br>[DPEN#] | 156     | [APICEN] |     | CLK        | 272     |         |     |  |

|     | V <sub>cc</sub> |            |          |     |      |          |      |     |          |      |     |      |     |  |  |  |

|-----|-----------------|------------|----------|-----|------|----------|------|-----|----------|------|-----|------|-----|--|--|--|

| 1*  | 35              | j          | 73       |     | 123  | 168*     | 190* | 230 |          | 257* |     | 295  |     |  |  |  |

| 2   | 41              | *          | 79       |     | 129  | 170*     | 195* | 232 | *        | 258  |     | 301  |     |  |  |  |

| 6*  | 43              | 3          | 85       |     | 135  | 172*     | 204  | 236 | i        | 260* |     | 304* |     |  |  |  |

| 11* | 49              | )*         | 91       |     | 141  | 174*     | 210  | 240 | *        | 264  |     | 306  |     |  |  |  |

| 17* | 51              |            | 97       |     | 147  | 177*     | 216  | 241 |          | 266* |     | 309* |     |  |  |  |

| 19  | 57              | <b>7</b> * | 103      |     | 153* | 178      | 217* | 243 | *        | 268* |     | 313  |     |  |  |  |

| 23  | 59              | )          | 109      |     | 157* | 180*     | 221  | 247 | •        | 275  |     | 317* |     |  |  |  |

| 27* | 65              | 5*         | 111*     |     | 160  | 183*     | 225* | 249 | *        | 281  |     |      |     |  |  |  |

| 33* | 67              | •          | 117      |     | 165* | 188*     | 226  | 253 |          | 291  |     |      |     |  |  |  |

|     |                 |            |          |     |      |          |      |     |          |      |     |      |     |  |  |  |

|     |                 |            |          |     |      | $V_{ss}$ |      |     |          |      |     |      |     |  |  |  |

| 3   |                 | 50         |          | 104 |      | 166      | 209  |     | 250      |      | 30  | 2    |     |  |  |  |

| 7   |                 | 52         |          | 110 |      | 169      | 215  |     | 252      |      | 30  | 5    |     |  |  |  |

| 12  |                 | 58         |          | 112 |      | 171      | 218  |     | 256      |      | 30  | 7    |     |  |  |  |

| 18  |                 | 60         |          | 118 |      | 173      | 220  |     | 261      |      | 31  | 0    |     |  |  |  |

| 20  |                 |            |          | 124 |      | 176      | 224  |     | 263      |      | 31  | 4    |     |  |  |  |

| 24  |                 | 68 1       |          | 130 |      | 179      | 229  |     | 267      |      | 32  |      |     |  |  |  |

| 26  |                 | 74         |          | 136 |      | 182      | 233  |     | 269      |      | -   |      |     |  |  |  |

| 32  |                 | 80         |          | 142 |      |          | 235  |     | 274      |      |     |      |     |  |  |  |

|     |                 |            |          |     |      | 187      |      |     |          |      |     |      |     |  |  |  |

| 36  |                 | 86         |          | 148 |      | 189      | 239  |     | 280      |      |     |      |     |  |  |  |

| 42  |                 | 92         | 154      |     | 154  |          | 154  |     |          | 194  | 244 |      | 290 |  |  |  |

| 44  |                 | 98 15      |          | 159 |      | 203      | 246  |     | 294      |      |     |      |     |  |  |  |

|     |                 |            |          |     |      | NC       |      |     |          |      |     |      |     |  |  |  |

| 175 |                 | 184        | <u> </u> | 185 | •    | 271      |      |     | <u> </u> |      |     |      |     |  |  |  |

Table 2. TCP Pin Cross Reference by Pin Name (Contd.)

#### NOTE:

\*These  $V_{CC}$  pins are 3.3V supplies for the Pentium processor (610\75) TCP but will be lower voltage pins on future offerings of this microprocessor family. All other  $V_{CC}$  pins will remain at 3.3V.

### 3.2. Design Notes

For reliable operation, always connect unused inputs to an appropriate signal level. Unused active low inputs should be connected to  $V_{\rm cc}$ . Unused active HIGH inputs should be connected to GND  $(V_{\rm ss})$ .

No Connect (NC) pins must remain unconnected. Connection of NC pins may result in component failure or incompatibility with processor steppings.

#### 3.3. Quick Pin Reference

This section gives a brief functional description of each of the pins. For a detailed description, see the "Hardware Interface" chapter in the *Pentium*® *Processor Family Developer's Manual*, *Volume 1*.

Note that all input pins must meet their AC/DC specifications to guarantee proper functional behavior.

The # symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage. When a # symbol is not present after the signal name, the signal is active, or asserted at the high voltage level.

Table 3. Quick Pin Reference

| Symbol                 | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M#                  | I        | When the <b>address bit 20 mask</b> pin is asserted, the Pentium processor (610\75) emulates the address wraparound at 1 Mbyte which occurs on the 8086. When A20M# is asserted, the Pentium processor (610\75) masks physical address bit 20 (A20) before performing a lookup to the internal caches or driving a memory cycle on the bus. The effect of A20M# is undefined in protected mode. A20M# must be asserted only when the processor is in real mode. |

| A31-A3                 | I/O      | As outputs, the <b>address</b> lines of the processor along with the byte enables define the physical area of memory or I/O accessed. The external system drives the inquire address to the processor on A31-A5.                                                                                                                                                                                                                                                |

| ADS#                   | 0        | The <b>address status</b> indicates that a new valid bus cycle is currently being driven by the Pentium processor (610\75) .                                                                                                                                                                                                                                                                                                                                    |

| AHOLD                  | I        | In response to the assertion of <b>address hold</b> , the Pentium processor (610\75) will stop driving the address lines (A31-A3), and AP in the next clock. The rest of the bus will remain active so data can be returned or driven for previously issued bus cycles.                                                                                                                                                                                         |

| АР                     | I/O      | Address parity is driven by the Pentium processor (610\75) with even parity information on all Pentium processor (610\75) generated cycles in the same clock that the address is driven. Even parity must be driven back to the Pentium processor (610\75) during inquire cycles on this pin in the same clock as EADS# to ensure that correct parity check status is indicated by the Pentium processor (610\75).                                              |

| APCHK#                 | 0        | The <b>address parity check</b> status pin is asserted two clocks after EADS# is sampled active if the Pentium processor (610\75) has detected a parity error on the address bus during inquire cycles. APCHK# will remain active for one clock each time a parity error is detected.                                                                                                                                                                           |

| [APICEN]<br>PICD1      | I        | The Advanced Programmable Interrupt Controller Enable pin enables or disables the on-chip APIC interrupt controller. If sampled high at the falling edge of RESET, the APIC is enabled. APICEN shares a pin with the Programmable Interrupt Controller Data 1 signal.                                                                                                                                                                                           |

| BE7#-BE5#<br>BE4#-BE0# | O<br>I/O | The <b>byte enable</b> pins are used to determine which bytes must be written to external memory, or which bytes were requested by the CPU for the current cycle. The byte enables are driven in the same clock as the address lines (A31-3).                                                                                                                                                                                                                   |

|                        |          | The lower four byte enables (BE3#-BE0#) are used on the Pentium processor (610\75) as APIC ID inputs and are sampled at RESET.                                                                                                                                                                                                                                                                                                                                  |

Table 3. Quick Pin Reference (Contd.)

| Symbol                | Type | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [BF]                  | I    | <b>Bus Frequency</b> determines the bus-to-core frequency ratio. BF is sampled at RESET, and cannot be changed until another non-warm (1 ms) assertion of RESET. Additionally, BF must not change values while RESET is active. For proper operation of the Pentium processor (610\75) this pin should be strapped high or low. When BF is strapped to V $_{\rm cc}$ , the processor will operate at a 2/3 bus/core frequency ratio. When BF is strapped to V $_{\rm ss}$ , the processor will operate at a 1/2 bus/core frequency ratio. If BF is left floating, the Pentium processor (610\75) defaults to a 2/3 bus ratio. Note the Pentium processor (610\75) will not operate at a 1/2 bus/core frequency ratio. |

| BOFF#                 | I    | The <b>backoff</b> input is used to abort all outstanding bus cycles that have not yet completed. In response to BOFF#, the Pentium processor (610\75) will float all pins normally floated during bus hold in the next clock. The processor remains in bus hold until BOFF# is negated, at which time the Pentium processor (610\75) restarts the aborted bus cycle(s) in their entirety.                                                                                                                                                                                                                                                                                                                            |

| BP[3:2]<br>PM/BP[1:0] | 0    | The <b>breakpoint</b> pins (BP3-0) correspond to the debug registers, DR3-DR0. These pins externally indicate a breakpoint match when the debug registers are programmed to test for breakpoint matches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                       |      | BP1 and BP0 are multiplexed with the <b>performance monitoring</b> pins (PM1 and PM0). The PB1 and PB0 bits in the Debug Mode Control Register determine if the pins are configured as breakpoint or performance monitoring pins. The pins come out of RESET configured for performance monitoring.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BRDY#                 | I    | The <b>burst ready</b> input indicates that the external system has presented valid data on the data pins in response to a read or that the external system has accepted the Pentium processor (610\75) data in response to a write request. This signal is sampled in the T2, T12 and T2P bus states.                                                                                                                                                                                                                                                                                                                                                                                                                |

| BREQ                  | 0    | The <b>bus request</b> output indicates to the external system that the Pentium processor (610\75) has internally generated a bus request. This signal is always driven whether or not the Pentium processor (610\75) is driving its bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BUSCHK#               | I    | The <b>bus check</b> input allows the system to signal an unsuccessful completion of a bus cycle. If this pin is sampled active, the Pentium processor (610\75) will latch the address and control signals in the machine check registers. If, in addition, the MCE bit in CR4 is set, the Pentium processor (610\75) will vector to the machine check exception.                                                                                                                                                                                                                                                                                                                                                     |

| CACHE#                | 0    | For Pentium processor (610\75)-initiated cycles the <b>cache</b> pin indicates internal cacheability of the cycle (if a read), and indicates a burst writeback cycle (if a write). If this pin is driven inactive during a read cycle, the Pentium processor (610\75) will not cache the returned data, regardless of the state of the KEN# pin. This pin is also used to determine the cycle length (number of transfers in the cycle).                                                                                                                                                                                                                                                                              |

Table 3. Quick Pin Reference (Contd.)

| Symbol           | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK              | I    | The <b>clock</b> input provides the fundamental timing for the Pentium processor (610\75). Its frequency is the operating frequency of the Pentium processor (610\75) external bus and requires TTL levels. All external timing parameters except TDI, TDO, TMS, TRST#, and PICD0-1 are specified with respect to the rising edge of CLK.                                                                                                                                                             |

| D/C#             | 0    | The <b>data/code</b> output is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. D/C# distinguishes between data and code or special cycles.                                                                                                                                                                                                                                                                                         |

| D63-D0           | I/O  | These are the 64 <b>data lines</b> for the processor. Lines D7-D0 define the least significant byte of the data bus; lines D63-D56 define the most significant byte of the data bus. When the CPU is driving the data lines, they are driven during the T2, T12, or T2P clocks for that cycle. During reads, the CPU samples the data bus when BRDY# is returned.                                                                                                                                     |

| DP7-DP0          | I/O  | These are the <b>data parity</b> pins for the processor. There is one for each byte of the data bus. They are driven by the Pentium processor (610\75) with even parity information on writes in the same clock as write data. Even parity information must be driven back to the Pentium processor (610\75) on these pins in the same clock as the data to ensure that the correct parity check status is indicated by the Pentium processor (610\75). DP7 applies to D63-D56; DP0 applies to D7-D0. |

| [DPEN#]<br>PICD0 | I/O  | <b>Dual processing enable</b> is an output of the Dual processor and an input of the Primary processor. The Dual processor drives DPEN# low to the Primary processor at RESET to indicate that the Primary processor should enable dual processor mode. Since the dual processing feature is not supported on the Pentium processor (610\75) TCP package, DPEN# should never be asserted (low) at RESET. DPEN# shares a pin with PICD0.                                                               |

| EADS#            | I    | This signal indicates that a valid <b>external address</b> has been driven onto the Pentium processor (610\75) address pins to be used for an inquire cycle.                                                                                                                                                                                                                                                                                                                                          |

| EWBE#            | I    | The external write buffer empty input, when inactive (high), indicates that a write cycle is pending in the external system. When the Pentium processor (610\75) generates a write, and EWBE# is sampled inactive, the Pentium processor (610\75) will hold off all subsequent writes to all E- or M-state lines in the data cache until all write cycles have completed, as indicated by EWBE# being active.                                                                                         |

| FERR#            | 0    | The <b>floating point error</b> pin is driven active when an unmasked floating point error occurs. FERR# is similar to the ERROR# pin on the Intel387 <sup>™</sup> math coprocessor. FERR# is included for compatibility with systems using DOS-type floating point error reporting.                                                                                                                                                                                                                  |

Table 3. Quick Pin Reference (Contd.)

| Symbol | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLUSH# | I    | When asserted, the <b>cache flush</b> input forces the Pentium processor (610\75) to write back all modified lines in the data cache and invalidate its internal caches. A Flush Acknowledge special cycle will be generated by the Pentium processor (610\75) indicating completion of the writeback and invalidation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        |      | If FLUSH# is sampled low when RESET transitions from high to low, tristate test mode is entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HIT#   | 0    | The <b>hit</b> indication is driven to reflect the outcome of an inquire cycle. If an inquire cycle hits a valid line in either the Pentium processor (610\75) data or instruction cache, this pin is asserted two clocks after EADS# is sampled asserted. If the inquire cycle misses the Pentium processor (610\75) cache, this pin is negated two clocks after EADS#. This pin changes its value only as a result of an inquire cycle and retains its value between the cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HITM#  | 0    | The <b>hit to a modified line</b> output is driven to reflect the outcome of an inquire cycle. It is asserted after inquire cycles which resulted in a hit to a modified line in the data cache. It is used to inhibit another bus master from accessing the data until the line is completely written back.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HLDA   | 0    | The <b>bus hold acknowledge</b> pin goes active in response to a hold request driven to the processor on the HOLD pin. It indicates that the Pentium processor (610\75) has floated most of the output pins and relinquished the bus to another local bus master. When leaving bus hold, HLDA will be driven inactive and the Pentium processor (610\75) will resume driving the bus. If the Pentium processor (610\75) has a bus cycle pending, it will be driven in the same clock that HLDA is de-asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HOLD   | I    | In response to the <b>bus hold request</b> , the Pentium processor (610\75) will float most of its output and input/output pins and assert HLDA after completing all outstanding bus cycles. The Pentium processor (610\75) will maintain its bus in this state until HOLD is de-asserted. HOLD is not recognized during LOCK cycles. The Pentium processor (610\75) will recognize HOLD during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IERR#  | 0    | The <b>internal error</b> pin is used to indicate internal parity errors. If a parity error occurs on a read from an internal array, the Pentium processor (610\75) will assert the IERR# pin for one clock and then shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| IGNNE# | I    | This is the <b>ignore numeric error</b> input. This pin has no effect when the NE bit in CR0 is set to 1. When the CR0.NE bit is 0, and the IGNNE# pin is asserted, the Pentium processor (610\75) will ignore any pending unmasked numeric exception and continue executing floating-point instructions for the entire duration that this pin is asserted. When the CR0.NE bit is 0, IGNNE# is not asserted, a pending unmasked numeric exception exists (SW.ES = 1), and the floating-point instruction is one of FINIT, FCLEX, FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium processor (610\75) will execute the instruction in spite of the pending exception. When the CR0.NE bit is 0, IGNNE# is not asserted, a pending unmasked numeric exception exists (SW.ES = 1), and the floating-point instruction is one other than FINIT, FCLEX, FSTENV, FSAVE, FSTSW, FSTCW, FENI, FDISI, or FSETPM, the Pentium processor (610\75) will stop execution and wait for an external interrupt. |

Table 3. Quick Pin Reference (Contd.)

| Symbol       | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT         | I    | The Pentium processor (610\75) <b>initialization</b> input pin forces the Pentium processor (610\75) to begin execution in a known state. The processor state after INIT is the same as the state after RESET except that the internal caches, write buffers, and floating point registers retain the values they had prior to INIT. INIT may NOT be used in lieu of RESET after power up.                                                                     |

|              |      | If INIT is sampled high when RESET transitions from high to low, the Pentium processor (610\75) will perform built-in self test prior to the start of program execution.                                                                                                                                                                                                                                                                                       |

| INTR / LINTO | I    | An active <b>maskable interrupt</b> input indicates that an external interrupt has been generated. If the IF bit in the EFLAGS register is set, the Pentium processor (610\75) will generate two locked interrupt acknowledge bus cycles and vector to an interrupt handler after the current instruction execution is completed. INTR must remain active until the first interrupt acknowledge cycle is generated to assure that the interrupt is recognized. |

|              |      | If the local APIC is enabled, this pin becomes local interrupt 0.                                                                                                                                                                                                                                                                                                                                                                                              |

| INV          | I    | The <b>invalidation</b> input determines the final cache line state (S or I) in case of an inquire cycle hit. It is sampled together with the address for the inquire cycle in the clock EADS# is sampled active.                                                                                                                                                                                                                                              |

| KEN#         | I    | The <b>cache enable</b> pin is used to determine whether the current cycle is cacheable or not and is consequently used to determine cycle length. When the Pentium processor (610\75) generates a cycle that can be cached (CACHE# asserted) and KEN# is active, the cycle will be transformed into a burst line fill cycle.                                                                                                                                  |

| LINTO/INTR   | I    | If the APIC is enabled, this pin is <b>local interrupt 0</b> . If the APIC is disabled, this pin is <b>interrupt</b> .                                                                                                                                                                                                                                                                                                                                         |

| LINT1/NMI    | I    | If the APIC is enabled, this pin is <b>local interrupt 1</b> . If the APIC is disabled, this pin is <b>non-maskable interrupt</b> .                                                                                                                                                                                                                                                                                                                            |

| LOCK#        | 0    | The <b>bus lock</b> pin indicates that the current bus cycle is locked. The Pentium processor (610\75) will not allow a bus hold when LOCK# is asserted (but AHOLD and BOFF# are allowed). LOCK# goes active in the first clock of the first locked bus cycle and goes inactive after the BRDY# is returned for the last locked bus cycle. LOCK# is guaranteed to be de-asserted for at least one clock between back-to-back locked cycles.                    |

| M/IO#        | 0    | The <b>memory/input-output</b> is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. M/IO# distinguishes between memory and I/O cycles.                                                                                                                                                                                                                                                        |

Table 3. Quick Pin Reference (Contd.)

| Symbol                         | Type | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NA#                            | I    | An active <b>next address</b> input indicates that the external memory system is ready to accept a new bus cycle although all data transfers for the current cycle have not yet completed. The Pentium processor (610\75) will issue ADS# for a pending cycle two clocks after NA# is asserted. The Pentium processor (610\75) supports up to 2 outstanding bus cycles.                                                                                                                                                                                                                 |

| NMI/LINT1                      | 1    | The <b>non-maskable interrupt</b> request signal indicates that an external non-maskable interrupt has been generated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                |      | If the local APIC is enabled, this pin becomes local interrupt 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PCD                            | 0    | The <b>page cache disable</b> pin reflects the state of the PCD bit in CR3, the Page Directory Entry, or the Page Table Entry. The purpose of PCD is to provide an external cacheability indication on a page-by-page basis.                                                                                                                                                                                                                                                                                                                                                            |

| PCHK#                          | 0    | The <b>parity check</b> output indicates the result of a parity check on a data read. It is driven with parity status two clocks after BRDY# is returned. PCHK# remains low one clock for each clock in which a parity error was detected. Parity is checked only for the bytes on which valid data is returned.                                                                                                                                                                                                                                                                        |

| PEN#                           | ı    | The <b>parity enable</b> input (along with CR4.MCE) determines whether a machine check exception will be taken as a result of a data parity error on a read cycle. If this pin is sampled active in the clock a data parity error is detected, the Pentium processor (610\75) will latch the address and control signals of the cycle with the parity error in the machine check registers. If, in addition, the machine check enable bit in CR4 is set to "1", the Pentium processor (610\75) will vector to the machine check exception before the beginning of the next instruction. |

| PICCLK                         | I    | The APIC interrupt controller serial data bus clock is driven into the <b>programmable interrupt controller clock</b> input of the Pentium processor (610\75).                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PICD0-1<br>[DPEN#]<br>[APICEN] | I/O  | <b>Programmable interrupt controller data lines 0-1</b> of the Pentium processor (610\75) comprise the data portion of the APIC 3-wire bus. They are opendrain outputs that require external pull-up resistors. These signals share pins with DPEN# and APICEN.                                                                                                                                                                                                                                                                                                                         |

| PM/BP[1:0]                     | 0    | These pins function as part of the performance monitoring feature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                |      | The breakpoint 1-0 pins are multiplexed with the <b>performance monitoring 1-0</b> pins. The PB1 and PB0 bits in the Debug Mode Control Register determine if the pins are configured as breakpoint or performance monitoring pins. The pins come out of RESET configured for performance monitoring.                                                                                                                                                                                                                                                                                   |

| PRDY                           | 0    | The <b>probe ready</b> output pin indicates that the processor has stopped normal execution in response to the R/S# pin going active, or Probe Mode being entered.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PWT                            | 0    | The <b>page writethrough</b> pin reflects the state of the PWT bit in CR3, the page directory entry, or the page table entry. The PWT pin is used to provide an external writeback indication on a page-by-page basis.                                                                                                                                                                                                                                                                                                                                                                  |

Table 3. Quick Pin Reference (Contd.)

| Type | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I    | The <b>run / stop</b> input is an asynchronous, edge-sensitive interrupt used to stop the normal execution of the processor and place it into an idle state. A high to low transition on the R/S# pin will interrupt the processor and cause it to stop execution at the next instruction boundary.                                                                                                                                                                                    |

| I    | RESET forces the Pentium processor (610\75) to begin execution at a known state. All the Pentium processor (610\75) internal caches will be invalidated upon the RESET. Modified lines in the data cache are not written back. FLUSH# and INIT are sampled when RESET transitions from high to low to determine if tristate test mode will be entered, or if BIST will be run.                                                                                                         |

| 0    | The <b>split cycle</b> output is asserted during misaligned LOCKed transfers to indicate that more than two cycles will be locked together. This signal is defined for locked cycles only. It is undefined for cycles which are not locked.                                                                                                                                                                                                                                            |

| Ι    | The <b>system management interrupt</b> causes a system management interrupt request to be latched internally. When the latched SMI# is recognized on an instruction boundary, the processor enters System Management Mode.                                                                                                                                                                                                                                                             |

| 0    | An active <b>system management interrupt active</b> output indicates that the processor is operating in System Management Mode.                                                                                                                                                                                                                                                                                                                                                        |

| I    | Assertion of the <b>stop clock</b> input signifies a request to stop the internal clock of the Pentium processor (610\75) thereby causing the core to consume less power. When the CPU recognizes STPCLK#, the processor will stop execution on the next instruction boundary, unless superseded by a higher priority interrupt, and generate a Stop Grant Acknowledge cycle. When STPCLK# is asserted, the Pentium processor (610\75) will still res pond to external snoop requests. |

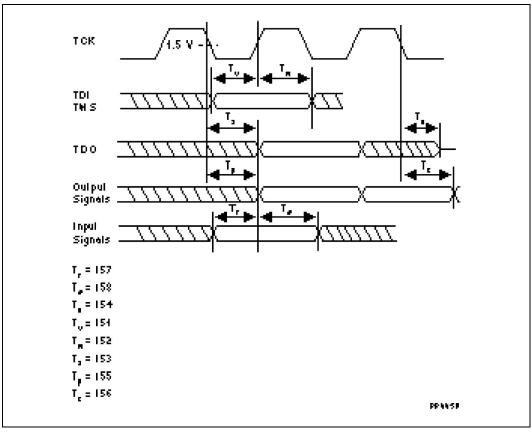

| I    | The <b>testability clock</b> input provides the clocking function for the Pentium processor (610\75) boundary scan in accordance with the IEEE Boundary Scan interface (Standard 1149.1). It is used to clock state information and data into and out of the Pentium processor (610\75) during boundary scan.                                                                                                                                                                          |

| I    | The <b>test data input</b> is a serial input for the test logic. TAP instructions and data are shifted into the Pentium processor (610\75) on the TDI pin on the rising edge of TCK when the TAP controller is in an appropriate state.                                                                                                                                                                                                                                                |

| 0    | The <b>test data output</b> is a serial output of the test logic. TAP instructions and data are shifted out of the Pentium processor (610\75) on the TDO pin on TCK's falling edge when the TAP controller is in an appropriate state.                                                                                                                                                                                                                                                 |

| I    | The value of the <b>test mode select</b> input signal sampled at the rising edge of TCK controls the sequence of TAP controller state changes.                                                                                                                                                                                                                                                                                                                                         |

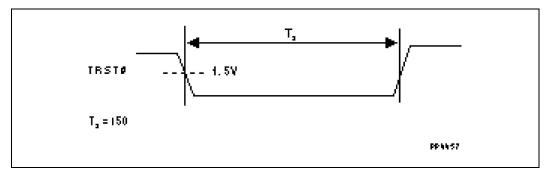

| I    | When asserted, the <b>test reset</b> input allows the TAP controller to be asynchronously initialized.                                                                                                                                                                                                                                                                                                                                                                                 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 3. Quick Pin Reference (Contd.)

| Symbol          | Туре | Name and Function                                                                                                                                                                                                                 |  |  |  |  |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>cc</sub> | I    | The Pentium processor (610\75) has 79 3.3V <b>power</b> inputs.                                                                                                                                                                   |  |  |  |  |

| V <sub>ss</sub> | I    | The Pentium processor (610\75) has 72 <b>ground</b> inputs.                                                                                                                                                                       |  |  |  |  |

| W/R#            | 0    | Write/read is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. W/R# distinguishes between write and read cycles.                                                |  |  |  |  |

| WB/WT#          | I    | The writeback/writethrough input allows a data cache line to be defined as writeback or writethrough on a line-by-line basis. As a result, it determines whether a cache line is initially in the S or E state in the data cache. |  |  |  |  |

#### 3.4. Pin Reference Tables

Table 4. Output Pins

| Name                    | Active Level | When Floated                            |

|-------------------------|--------------|-----------------------------------------|

| ADS#                    | Low          | Bus Hold, BOFF#                         |

| APCHK#                  | Low          |                                         |

| BE7#-BE5#               | Low          | Bus Hold, BOFF#                         |